DRAM Self-Refreshing Technology

The Random Access Memory (RAM) in a PC is required to continuously self-refresh to maintain a healthy charge level in all the capacitors even when no data is being read. Due to the nature of this design and the materials used, the electrical charge in the capacitors will gradually leak out over time. Eventually, it gets to a point where the data cannot be held reliably so the power must be refreshed.This is the main difference between RAM and non-volatile memories such as Read Only Memory (ROM) or Flash (NAND or NOR). In mobile devices such as notebooks and handhelds, this self-refreshing nature is modified to further reduce power consumption, thus prolonging battery life.

The following sections describe four different methods of saving power used by mobile DDR.

- Temperature Compensated Self-Refresh

- Partial Array Self-Refresh

- Deep Power Down

- Clock Stop Mode

Temperature Compensated Self-Refresh (TCSR)

Temperature Compensated Self-Refresh is mostly found in SO-DIMM. DDR1 and DDR2 have a single self-refresh mode and DDR3 has enhanced the technique by having two temperature sensitive self-refresh modes. When DDR3 temperature is below 85˚C (185˚F), the refresh interval is set to 7.8µs. If the operating temperature is between 85˚C (185˚F) and 95˚C (203˚F), the refresh interval is required to drop to 3.9µs (twice as fast).The idea is based on the principle that the amount of time DRAM can retain data is directly related to the operating temperature. Higher temperatures will cause DRAM to lose the data faster as a result of charge leakage. Hence, more self-refresh sessions are required in a given period to keep the data in a healthy state.

When the temperature is lower, the self-refreshing period can be longer, so in theory, when DDR3 is operating below 85˚C (185˚F), it could potentially save close to 50 percent on the power consumption front. With desktop memory modules, it is rare to have the temperature of DIMMs running above 60˚C (140˚F) because there is generally more space for better cooling to be applied.

The refresh interval may differ slightly between DRAM manufacturers – it is dependent on the circuitry and chip fabrication technology used by individual company, but this difference might also contribute to some compatibility issues between mobile memory and device BIOS. Some manufacturers may also implement this feature slightly differently depending on where they place or use the temperature sensor; on-die or on-DIMM – on-die specifically detects the memory core temperature, whereas on-DIMM detects the environment temperature.

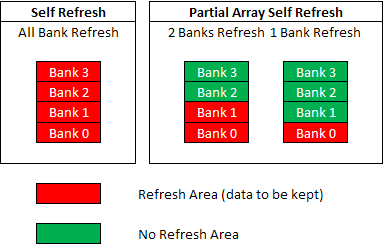

Partial Array Self-Refresh (PASR)

Within the DRAM chip, there are memory banks that are structured with columns and rows, similar to the worksheets in a spreadsheet programme like Microsoft Excel. With PASR, the DRAM is pre-programmed with certain self-refresh behaviours in addressing these columns and rows in order to reduce power consumption.For example:

- Full Array: Banks 0, 1, 2, and 3

- Half Array: Banks 0 and 1

- 1/4 Array: Bank 0

- 1/8 Array: Bank 0 with row address MSB = 0

- 1/16 Array: Bank 0 with row address MSB and MSB-1 both equal to zero

Overview of Self-Refresh and Partial Array Self Refresh modes

Source: Elpida Memory

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.